Nov 4, 2017 - ones = 0; //initialize count variable. If(Ai 1'b1) //check if the bit is '1' ones = ones + 1; //if its one,. 4 bit counter connected to the LEDs. To count more slowly, the clock signal of the counter is passed through a 22 bit prescaler. This is the same counter as in Chapter 4, but with an improved design: to change the frequency of the counter, just change the parameter of the prescaler (and no need to modify the width of the counter or reassign them in the.pcf file).

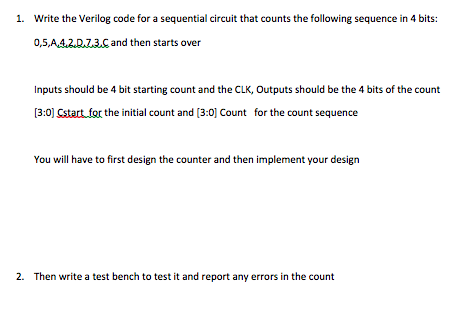

Introduction

4 bit counter connected to the LEDs. To count more slowly, the clock signal of the counter is passed through a 22 bit prescaler. This is the same counter as in Chapter 4, but with an improved design: to change the frequency of the counter, just change the parameter of the prescaler (and no need to modify the width of the counter or reassign them in the .pcf file).

Hardware Description

The counter has a clock input and a 4-bit data output. It also has parameter N to indicate the number of bits of the prescaler and set it's operating frequency. The verilog code is as follows:

You could have defined a generic counter in a seperate file and instantiate it (just like you did with the prescaler). However, in this case this is to show an example of hierarchical design mixed with a component defined in a process. In addition, the counter is so simple that it is not worth it to store in a seperate file.

The code has been implemented following the design in image 1.

Synthesis of the FPGA

The 12 Mhz clock signal enters the FPGA via pin 21, and the output data is sent to each pin connected to the LEDs, from 99 to 96.

to synthesis the design, execute the command:

The resources used are:

| Resources | utilization |

|---|---|

| PIOs | 3 / 96 |

| PLBs | 8 / 160 |

| BRAMs | 0 / 16 |

Load the design into the fpga with the command:

Simulation

The testbench is similar to Chapter 4, but the counter test process has been slightly modified. Now instead of performing the check on the falling edge, it is done when any change occurs in the data output of the counter. This is accomplished by putting data in the sensitivity list of the checking process.

The verification process begins with

This means it runs every time there is a change in

data

To simulate we execute:

The result is:

We see that the counter is counting. a 1 bit prescaler was used to make this occur much faster in simulation.

Proposed exercises

- Change the prescaler to count faster.

- Change the counter to count down.

Conclusions

TODO